L’architecture et la conception du robot couvrent maintenant un large éventail de fonctions et de capacités. Cela a un fort impact sur la capacité du processeur, et sur ce qui est utilisé pour la fournir. Dans l’environnement contrôlé d’une cage de sécurité, un robot de production a besoin de relativement peu de mesures de protection et peut utiliser des stratégies de contrôle procédurales simples.

Les concepteurs doivent veiller à ce que le robot s’arrête si la cage est ouverte, ou si les pièces ne sont pas alignées comme prévu. De même, il est possible de surmonter de nombreuses difficultés en matière de sécurité à l’aide de simples verrouillages matériels, plutôt qu’avec des combinaisons complexes de capteurs d’image et de logiciels. Les principales exigences en matière de processeur sont d’assurer un contrôle efficace et précis des mouvements. Ceci demande notamment l’utilisation de microcontrôleurs ou de processeurs de signaux numériques pour gérer le flux de puissance vers les moteurs et autres actionneurs.

L’évolution des microcontrôleurs

Les conceptions de robot de production classique ont tendance à être inflexibles. Tous leurs programmes doivent être programmés, simulés et testés minutieusement avant que le robot soit autorisé à fonctionner. Dans le secteur de la fabrication, les utilisateurs souhaitent que les robots soient plus flexibles afin qu’ils puissent être rapidement affectés à différentes tâches. Ils doivent également être capables de se déplacer dans la zone de production, ce qui leur demande de fonctionner en dehors de la cage de sécurité. Ces exigences demandent une plus grande capacité du processeur pour que le robot puisse naviguer sans collision accidentelle avec des objets ou sans blesser de personnes spectatrices.

Par conséquent, les robots doivent être en mesure de traiter l’entrée de capteur en temps réel et de prendre des décisions intelligentes instantanées selon l’évolution de la situation. Plus les robots s’éloignent de la cage de sécurité, plus ils interagissent avec les humains et plus ils auront besoin d’une grande capacité de processeur. Ils évoluent en effet alors au-delà de l’environnement relativement contrôlé de l’atelier de fabrication. Les robots de service et les drones de livraison doivent être capables de réagir intelligemment à des situations complexes.

Dans ces scénarios plus complexes, une plus grande sophistication du logiciel est nécessaire, allant de pair avec le débit de calcul. Le concepteur dispose de nombreuses options pour fournir la capacité de processeur nécessaire, que ce soit en termes de fournisseurs ou d’architecture globale.

L’utilisation des microcontrôleurs

Le microcontrôleur (MCU) est depuis de nombreuses années l’élément de calcul de choix pour les robots de base. Le microprocesseur est le coeur de la MCU. A l’origine, les coeurs de microprocesseurs des MCU ont été optimisés pour un contrôle de niveau logique et une arithmétique simple. Mais depuis leur introduction il y a presque 50 ans, les capacités de performances et de traitement des données ont considérablement augmenté. Aujourd’hui, les coeurs de microprocesseurs qui fonctionnent en mots de données de 32 bits et offrent des fonctionnalités performantes telles que le pipeline et l’architecture de type Harvard, sont maintenant proposés à un coût permettant même à de simples systèmes de les utiliser.

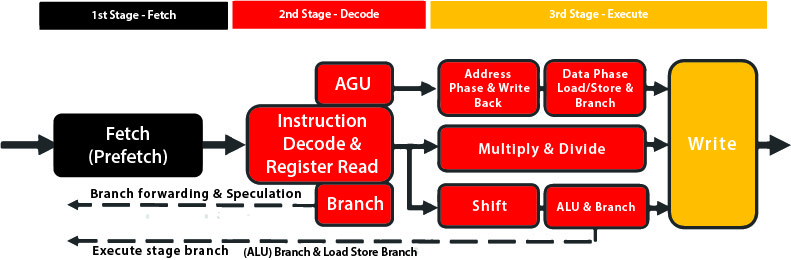

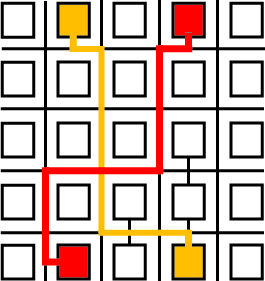

Dans un cœur de microprocesseur de 32 bits classique, tel que l’ARM Cortex-M3, un pipeline d’instruction sépare l’exécution de commandes en plusieurs phases. Dans le pipeline M3, l’instruction provient premièrement d’un cache local. Si l’instruction n’est pas dans le cache, elle doit d’abord être chargée à partir de la mémoire principale. Une fois dans le pipeline, les octets d’instruction sont décodés pour évaluer les unités fonctionnelles qui doivent être activées pour exécuter l’instruction. Enfin, l’exécution a lieu.

Le pipeline et le traitement des interruptions

Le pipeline est utilisé pour masquer des effets comme la latence de la mémoire. Il permet d’exécuter plusieurs instructions se chevauchant et augmente la vitesse d’horloge puisque moins d’étapes logiques sont nécessaires par cycle. Les cœurs de processeur plus rapides utilisent des pipelines plus étendus qui peuvent comporter dix étapes ou plus. L’inconvénient des longs pipelines est une latence élevée en matière de branchement. Si un branchement est pris, il faut du temps pour recharger le pipeline avec les instructions nécessaires au nouveau branchement.

Le support lié aux interruptions permet au cœur du processeur de suspendre temporairement l’exécution du programme principal et de gérer d’autres tâches. La gestion des interruptions est un élément clé des applications qui ont besoin de réponse aux événements en temps réel. Sans elle, le code du programme devrait contenir des boucles sondant en continu les informations concernant des événements externes, ce qui provoquerait un plus grand gaspillage de la capacité de calcul.

Microprocesseurs pour les concepteurs de robots

Un schéma de priorité employé par la plupart des cœurs de processeur permet d’interrompre des périphériques relativement peu importants pouvant être ignorés, pendant que le processeur gère les opérations courantes critiques, telles que le transfert de contrôle d’une tâche à l’autre, ou l’entrée d’une interruption critique. Il en résulte une architecture hautement flexible qui peut traiter de nombreux types d’applications en temps réel.

Une version spécialisée importante du microprocesseur pour les concepteurs de robot est le processeur de signal numérique (DSP). Il s’agit d’un cœur de processeur qui fournit des instructions et du matériel d’exécution optimisé pour les algorithmes de traitement de signaux tels que les filtres et les transformations de Fourier rapides. De telles instructions comprennent des opérations rapides de «fused multiply-add» (FMA), présentes dans pratiquement tous les algorithmes DSP. Comme le code DSP fonctionne sur des structures de données telles que des matrices et des vecteurs, il est relativement facile de paralléliser le travail. Cela a conduit à l’implémentation d’unités d’exécution SIMD (à instruction simple et données multiples) qui effectuent les mêmes opérations, comme les opérations multiply-add, pour plusieurs éléments d’un tableau en même temps. Le résultat est une vitesse beaucoup plus grande pour une complexité et un coût supplémentaires limités.

Un microcontrôleur comprend un certain nombre de périphériques intégrés qui sont organisés autour du coeur du processeur. Généralement, dans un microcontrôleur industriel ou robotique, les périphériques varient des réseaux de mémoire aux unités de déclenchement de la temporisation avancées, utilisées pour soulager le microprocesseur de la modulation d’impulsion en durée (PWM). La PWM est un élément essentiel de presque toutes les stratégies de commande de moteur et elle occupe une place majeure dans la conception robotique. D’autres dispositifs system-on-chip (SoC) ajoutent des fonctionnalités autour d’un microcontrôleur telles que des émetteurs-récepteurs sans fil, un chiffrement dédié et une logique d’authentification, ainsi que des accélérateurs graphiques.

Contrôle et matériel

L’utilisation de périphériques intelligents souligne également un principe de conception de plus en plus important pour les robots: l’exploitation de commande répartie et l’accélération matérielle. Un microprocesseur peut être utilisé pour mettre en œuvre la commande PWM, mais cela signifie souvent une mauvaise allocation des ressources. Le problème principal est que le logiciel doit couper à plusieurs reprises le courant entre les transistors dans le demi-pont qui contrôle le débit de courant d’un moteur après des intervalles préprogrammés. Les interruptions d’une horloge ou d’un compteur temps réel peuvent facilement déclencher des gestionnaires pour qu’ils coupent l’alimentation, avant de configurer le minuteur pour le cycle suivant. Cela aboutit cependant à de fréquentes interruptions et donc à une séquence d’opérations extrêmement simple.

Un contrôleur PWM associe temporisation et logique de commutation, ce qui supprime le besoin d’interrompre le cœur de microprocesseur pour chaque opération de commutation. Le logiciel doit simplement mettre à jour régulièrement les temporisations pour définir le cycle opératoire PWM nécessaire. Grâce à une quantité relativement faible de logique supplémentaire qui peut fonctionner indépendamment du processeur pendant de longues périodes, l’efficacité du logiciel est grandement améliorée. L’architecture a des caractéristiques communes avec d’autres mécanismes de transfert du matériel qui deviendront de plus en plus importants dans la conception robotique. Les périphériques matériels prennent en charge des événements fréquents en temps réel, tandis que le logiciel définit une politique pour ces périphériques.

Avec les périphériques matériels, les concepteurs sont limités aux fonctions offertes par les fournisseurs de circuits intégrés, bien que l’intégration de séquenceurs fondés sur des machines à état matériel augmente leur flexibilité. Par exemple, ces séquenceurs peuvent lire les valeurs d’un convertisseur A/D, transférer les valeurs de données à la mémoire principale en utilisant l’accès direct à la mémoire (direct memory access ou DMA en anglais), ainsi que régler et recharger les minuteurs, sans jamais impliquer le cœur du processeur. Toutefois, les options restent limitées.

Le FPGA dans la robotique

Le réseau de portes programmables (FPGA) permet de créer des périphériques matériels personnalisés qui peuvent être optimisés pour des fonctions de contrôle robotique et d’apprentissage automatique.

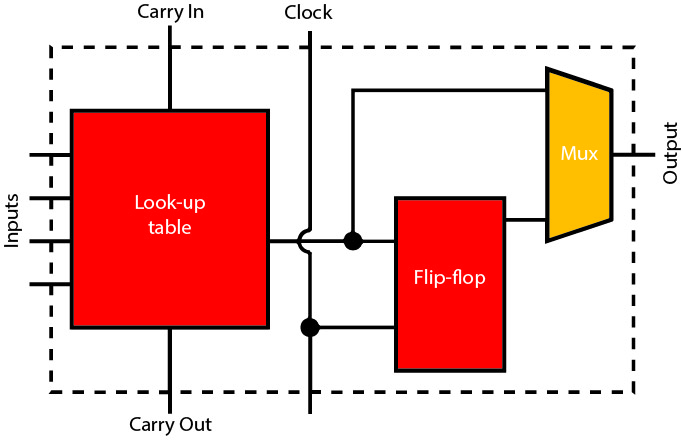

Le cœur de la plupart des architectures FPGA est un tableau de recherche programmable qui peut être configuré pour mettre en œuvre toute fonction logique pouvant s’exprimer sous la forme d’une table de vérité. En utilisant des commutateurs programmables dans la structure d’interconnexion, les tables de recherche sont connectées ensemble dans de complexes circuits logiques combinés. Généralement, chaque tableau de recherche est accompagné d’un ou de plusieurs registres et d’une logique de support supplémentaire, telles que des entrées et des sorties de la chaîne, afin de mettre en œuvre des additionneurs arithmétiques de manière efficace. Ensemble, ces fonctions forment un bloc logique qui est repris à plusieurs reprises dans le FPGA.

L’inconvénient par rapport à la logique entièrement personnalisée est que leur efficacité en silicium est beaucoup plus faible. Il faut 10 à 20 fois plus de zones de silicium pour loger un circuit logique sur une structure FPGA que pour une implémentation personnalisée et standard.

Cependant, la plupart des FPGA prennent en charge la reprogrammation du réseau logique, même dans un système en fonctionnement. Cela permet de partager les ressources en ne chargeant activement les accélérateurs dans la structure que lorsqu’ils sont nécessaires. Cette approche offre également une plus grande souplesse au niveau de la conception finale, en permettant de prendre en charge de nouveaux matériels et des fonctionnalités supplémentaires.

Depuis leur introduction dans les années 1980, les FPGA ont acquis d’autres caractéristiques qui améliorent la densité globale. Les blocs mémoire permettent la création de tampons et de caches proches de la logique programmable. Ils sont accompagnés depuis peu des moteurs DSP. Dans de nombreux cas, les moteurs DSP sont mis en œuvre à l’aide d’une approche de blocs de construction, composée d’unités de 8 bits ou 16 bits, qui permet de les combiner pour prendre en charge des types de données de haute précision.

Les unités DSP rendent le FPGA particulièrement approprié pour le traitement des entrées des capteurs qui produisent de grandes quantités de données, comme les caméras, les radars et d’autres types de capteurs d’image. Il est fréquent d’utiliser une combinaison d’unités DSP et d’accélérateurs logiques pour manipuler des algorithmes tels que la distorsion d’image et la compensation d’éclairage, qui fournissent des entrées plus cohérentes pour l’apprentissage automatique et pour des fonctions similaires. Ces fonctions peuvent être coordonnées par des coeurs de microprocesseurs personnalisés mis en oeuvre dans la structure programmable, qui agissent comme des microséquenceurs pour les processus primitifs.

Exploitation des processeurs graphiques (GPU), des unités de traitement de la vision (VPU) et des multiprocesseurs

Une autre option, en particulier pour les tâches de traitement d’images, consiste à employer un processeur graphique (GPU) ou des unités de traitement de la vision (VPU). Ces derniers contiennent des moteurs DSP hautement parallélisés et optimisés pour le traitement d’images. Pour les robots qui ont besoin de niveaux très élevés de sensibilisation à l’environnement, ces unités dédiées peuvent être combinées avec plusieurs CPU, parfois sur la même puce, comme un SoC multicœur hétérogène.

Le multiprocesseur peut également être utilisé pour améliorer la fiabilité et la sécurité globales. Sa dépendance à l’égard des technologies de mémoire vulnérables aux rayonnements ionisants est un problème qui concerne toutes les conceptions informatique. Lorsque le rayonnement ionisant frappe le substrat de silicium d’un circuit intégré, il déclenche une cascade d’électrons libres qui font basculer l’état logique d’un transistor. Dans les transistors à circuit combinatoire, l’effet est généralement transitoire et persiste rarement.

Toutefois, les mémoires et les registres sont plus vulnérables au changement en raison de la façon dont ils recyclent leur contenu pour empêcher la fuite des données stockées. Les codes de vérification et correction d’erreur (Error checking and correction ou ECC en anglais) permettent de contrôler ce problème. La probabilité d’une perturbation due à un seul événement augmente avec la densité de la mémoire, ce qui crée un problème croissant lorsque ces circuits intégrés continuent d’évoluer selon la loi de Moore. La vérification et correction d’erreur peut aussi ne pas distinguer toutes les erreurs. Dans ce cas, le programme agit sur des données incorrectes, ce qui finit par provoquer une défaillance au niveau du contrôle. Il ne faut pas que cela se produise pour un robot en interaction avec le public.

Techniques de redondance et conception de processeurs diversifiés

Des techniques fonctionnent, comme, par exemple, le traitement redondant du problème par des processeurs individuels qui vérifient les travaux de chacun.

Les processeurs peuvent être du même type et exécuter le même code. La vérification de la logique permet de comparer leurs sorties et utilise le vote pour déterminer l’opération à autoriser, ou pour demander d’exécuter à nouveau des opérations jusqu’à ce que les processeurs donnent leur accord.

L’utilisation de trois processeurs avec le vote à la majorité est plus chère mais moins intrusive, car les opérations de réexécution peuvent provoquer des retards non désirés. La redondance modulaire peut également être mise en œuvre au niveau de la porte.

Dans un accord redondant, les processeurs ne doivent pas être identiques. Certaines architectures ont un processeur moins performant qui agit comme un moteur de vérification. Plutôt que d’exécuter le même logiciel, il effectue tout simplement des contrôles de cohérence et impose une réexécution en cas d’échec d’une vérification ou, dans des cas plus extrêmes, une réinitialisation complète.

Pour minimiser les risques d’erreurs de conception systématiques dans l’équation, les processeurs dupliqués peuvent être conçus et mis en œuvre de différentes façons. Cette technique est utilisée sur certains SoC multicœurs mis au point pour des systèmes de sécurité automobile.

Options architecturales pour les concepteurs de robots

Grâce à cela, les concepteurs de robots peuvent maintenant choisir parmi un large éventail d’options architecturales allant de simples conceptions à des machines hautement flexibles qui peuvent réagir intelligemment à des problèmes et à des obstacles, et continuer à fonctionner efficacement.