Robotarkitektur og design dekker nå en rekke funksjoner. Dette påvirker i stor grad prosessorkraften og hva som brukes til å levere den. Innenfor de kontrollerte omgivelsene i et sikkerhetsbur trenger en produksjonsrobot relativt få sikkerhetstiltak og kan benytte seg av enkle prosedyremessige kontrollstrategier.

Utviklere må sørge for at roboten stopper hvis buret åpnes, eller hvis delene ikke er innrettet som forventet. Likevel kan mange av sikkerhetsutfordringene løses ved hjelp av enkle maskinvarelåser i stedet for komplekse kombinasjoner av bildesensorer og programvare. De viktigste prosesseringskravene er å sikre effektiv og presis bevegelsesstyring. Dette krever først og fremst bruk av mikrokontrollere eller digitale signalprosessorer for å styre strømmen til motorer og andre aktuatorer.

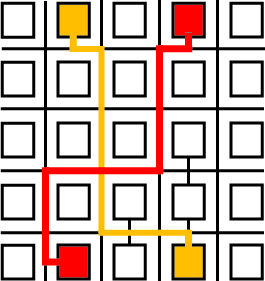

Utviklingen av mikrokontrollerenheter

Konvensjonelle produksjonsroboter er ikke ofte veldig fleksible. Hvert program må programmeres, simuleres og testes grundig før roboten får lov til å fortsette. I produksjonsindustrien ønsker brukerne at robotene skal være mer fleksible, slik at de raskt kan settes inn i ulike oppgaver. De må også kunne bevege seg rundt på produksjonsgulvet, noe som innebærer arbeid utenfor sikkerhetsburet. Disse kravene krever større prosessorkraft for å gi roboten mulighet til å navigere uten å kollidere med gjenstander eller skade tilskuere.

Derfor må robotene være i stand til å behandle sensordata i sanntid og ta intelligente beslutninger underveis når omstendighetene endrer seg. Jo lenger robotene beveger seg bort fra sikkerhetsburet og jo mer de samhandler med mennesker, desto mer prosessorkraft vil de trenge når de beveger seg utenfor det relativt kontrollerte miljøet på verkstedet. Serviceroboter og leveringsdroner må kunne reagere intelligent i komplekse situasjoner.

I disse mer avanserte scenariene er det et klart behov for mer sofistikert programvare, noe som går hånd i hånd med økt regnekapasitet. Utvikleren har stor valgfrihet med hensyn til hvordan den nødvendige prosessorkraften skal leveres, ikke bare når det gjelder leverandører, men også når det gjelder den overordnede arkitekturen.

Bruken av mikrokontrollere

Mikrokontrollerenheten (MCU) har i mange år vært det foretrukne beregningselementet for enkle roboter. Mikroprosessoren er kjernen av MCU-en. Disse ble først optimalisert for enkel aritmetikk og logisk styring, men siden de ble introdusert for snart 50 år siden har ytelsen og datahåndteringskapasiteten økt dramatisk. I dag fins det mikroprosessorkjerner som opererer på 32-bit dataord og som har ytelsesegenskaper som pipelining og Harvard-arkitektur, til en pris som gjør at selv enkle systemer kan bruke dem.

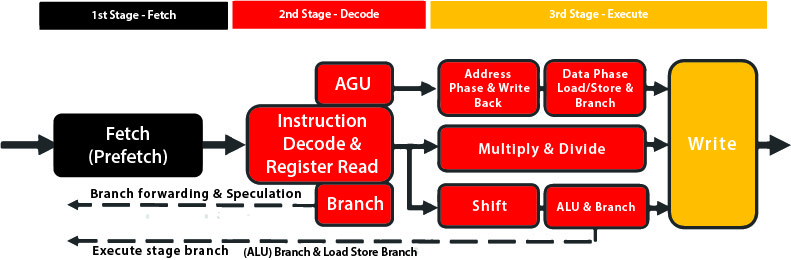

I en typisk 32-bit mikroprosessorkjerne, for eksempel ARM Cortex-M3, finnes det en instruksjonspipeline som deler opp utførelsen av kommandoer i flere faser. I M3-pipelinen hentes instruksjonen først fra en lokal hurtigbuffer. Hvis instruksjonen ikke finnes i hurtigbufferen, må den først lastes inn fra hovedminnet. I pipelinen dekodes instruksjonsbytene for å evaluere hvilke funksjonelle enheter som må aktiveres for å utføre instruksjonen. Til slutt skjer utførelsen.

Pipelining og avbruddshåndtering

Pipelining brukes til å skjule effekter som f.eks. latenstiden i minnet. Det gjør det mulig å overlappe utførelsen av flere instruksjoner og bidrar til å øke klokkehastigheten, ettersom det trengs færre logiske trinn per syklus. Raskere prosessorkjerner bruker mer omfattende pipelines som kan være ti trinn lange eller mer. Ulempen med lange pipelines er høy forgreningsforsinkelse. Hvis en forgrening tas, tar det tid å fylle opp pipelinen med instruksjonene som trengs for den nye forgreningen.

Støtte for avbrudd gjør det mulig for prosessorkjernen å avbryte kjøringen av hovedprogrammet midlertidig og håndtere andre oppgaver. Avbruddshåndtering er en nøkkelkomponent for applikasjoner som trenger sanntidsrespons på hendelser. Uten den ville programkoden måtte inneholde løkker som kontinuerlig søker etter informasjon om eksterne hendelser, noe som ville sløse mye mer med beregningskapasiteten.

Mikroprosessorer for robotdesignere

En prioritetsordning som brukes av de fleste prosessorkjerner, gjør at avbrudd fra relativt uviktige eksterne enheter kan ignoreres mens prosessoren tar seg av kritiske rutiner, for eksempel overføring av kontroll fra en oppgave til en annen eller input fra et kritisk avbrudd. Resultatet er en svært fleksibel arkitektur som kan håndtere mange ulike typer sanntidsapplikasjoner.

En viktig og spesialisert variant av mikroprosessoren for robotdesignere er den digitale signalprosessoren (DSP). Dette er en prosessorkjerne som inneholder instruksjoner og maskinvare som er optimalisert for signalbehandlingsalgoritmer som filtre og hurtige Fourier-transformasjoner. Slike instruksjoner inkluderer raske, sammensmeltede multiplikasjon-operasjoner som finnes i praktisk talt alle DSP-algoritmer. Fordi DSP-koder opererer på datastrukturer som matriser og vektorer, er det relativt enkelt å utføre arbeidet parallelt. Dette har ført til implementeringen av SIMD-enheter (single-instruction, multiple-data) som utfører de samme operasjonene – for eksempel multiplikasjon og addisjon – på flere elementer i en matrise samtidig. Resultatet er mye høyere hastighet til en relativt liten ekstra kompleksitet eller kostnad.

En MCU inneholder en rekke integrerte periferienheter som er plassert rundt prosessorkjernen. I en industri- eller robotorientert MCU er det vanlig at periferienhetene spenner fra minnematriser til avanserte timerutløserenheter, som brukes til å avlaste mikroprosessoren for pulsbreddemodulering (PWM). PWM er en kjernekomponent i nesten alle motorstyringsstrategier og har derfor en fremtredende plass i robotdesign. Andre SoC-enheter (system-on-chip) legger til flere funksjoner rundt MCU-en, for eksempel trådløse transceivere, dedikert krypterings- og autentiseringslogikk, og grafikkakseleratorer.

Styring og maskinvare

Bruken av intelligent periferiutstyr illustrerer også et stadig viktigere designprinsipp for roboter: utnyttelse av distribuert kontroll og maskinvareakselerasjon. En mikroprosessor kan brukes til å implementere PWM-styring, men det er ofte en dårlig ressursallokering. Hovedproblemet er at programvaren gjentatte ganger må bytte strøm mellom transistorene i halvbroen som styrer strømmen til en motor, etter forhåndsprogrammerte intervaller. Avbrudd fra en sanntidsklokke eller -teller kan enkelt utløse håndteringer for å skifte strømtilstand og deretter konfigurere timeren for neste syklus. Men dette resulterer i en høy avbruddsfrekvens for det som er en ekstremt enkel sekvens av operasjoner.

En PWM-kontroller kombinerer timer- og koblingslogikk, noe som fjerner kravet om at mikroprosessorkjernen må avbrytes for hver kobling. Programvaren trenger bare å oppdatere tidtakerne med jevne mellomrom for å stille inn ønsket PWM-driftssyklus. Takket være en forholdsvis liten mengde ekstra logikk som kan operere uavhengig av prosessoren i lange perioder, er programvarens effektivitet betydelig forbedret. Arkitekturen har en fellesnevner med andre avlastningsmekanismer som vil bli stadig viktigere i robotdesign. Maskinvareperiferiutstyr tar seg av hyppige hendelser i sanntid, mens programvaren fastsetter retningslinjene.

Utviklere er også begrenset til de funksjonene som IC-leverandørene tilbyr, selv om inkludering av sekvenser basert på maskinvaretilstandsmaskiner øker fleksibiliteten. Slike sequencere kan for eksempel lese verdier fra en A/D-omformer, overføre dataværdier til hovedminnet ved hjelp av direkte minnetilgang (DMA) og stille inn og laste inn tidtakere, alt uten å involvere CPU-kjernen. Alternativene er imidlertid fortsatt begrensede.

FPGA i robotikk

FPGA (Field Programmable Gate Array) gjør det mulig å lage spesialtilpasset maskinvareperiferiutstyr som kan optimaliseres for spesifikke robotstyrings- og maskinlæringsfunksjoner.

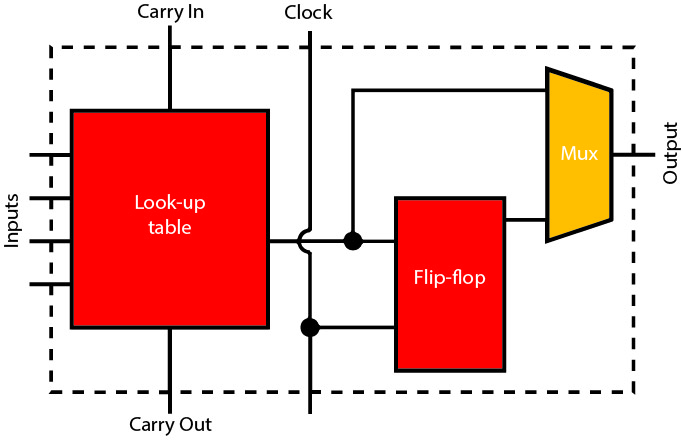

Kjernen i de fleste FPGA-arkitekturer er en programmerbar oppslagstabell som kan konfigureres til å implementere en hvilken som helst logisk funksjon som kan uttrykkes som en sannhetstabell. Ved hjelp av programmerbare brytere i sammenkoblingsstrukturen kobles oppslagstabellene sammen til komplekse kombinasjonslogiske kretser. Hver oppslagstabell ledsages vanligvis av ett eller flere registre og ekstra støttelogikk, for eksempel inn- og utganger for overføringskjeder, for å gjøre det mulig å implementere aritmetiske addere på en effektiv måte. Til sammen utgjør disse funksjonene en logikkblokk som replikeres mange ganger på tvers av FPGA-en.

En ulempe sammenlignet med fullt tilpasset logikk er at silisiumeffektiviteten er mye lavere. Det kreves 10 til 20 ganger så mye silisiumareal for å plassere en logisk krets på en FPGA sammenlignet med en tilpasset implementering med standardceller.

De fleste FPGA-er har imidlertid støtte for omprogrammering av logikkenheten selv i et system som er i drift. Dette gjør det mulig å dele ressurser ved at akseleratorer lastes dynamisk inn i nettverket bare når det er behov for dem. Denne tilnærmingen gir også større fleksibilitet i det endelige designet, slik at det kan støtte ny maskinvare og tilleggsfunksjoner.

Siden FPGA-ene ble introdusert på 1980-tallet, har de fått flere funksjoner som øker den totale tettheten. Minneblokker gjør det mulig å opprette buffere og hurtigbuffere i nærheten av den programmerbare logikken. I den senere tid har disse fått selskap av DSP-motorer. I mange tilfeller er DSP-motorene implementert ved hjelp av en byggeklosstilnærming, bestående av 8- eller 16-biters enheter, som gjør det mulig å kombinere dem for å støtte datatyper med høyere presisjon.

DSP-enheter gjør FPGA-er svært godt egnet til å behandle input fra sensorer som produserer store datamengder, for eksempel kameraer, radarer og andre typer bildesensorer. Et typisk bruksområde er å bruke en kombinasjon av DSP-enheter og logiske akseleratorer for å håndtere algoritmer som bildeforvridning og lyskompensasjon som gir mer konsistent input til maskinlæring og lignende funksjoner. Disse funksjonene kan koordineres av egendefinerte mikroprosessorkjerner som er implementert i den programmerbare strukturen, og som fungerer som mikrosekvenser for de ulike prosesseringsprimitivene.

Utnyttelse av GPU-er, VPU-er og multiprosessering

Et annet alternativ, spesielt for bildebehandlingsoppgaver, er å bruke en grafikkprosessorenhet (GPU) eller en synsprosessorenhet (VPU). Disse inneholder høyparallelliserte DSP-motorer som er optimalisert for bildebehandling. For roboter som trenger svært høy grad av miljøbevissthet, kan disse dedikerte enhetene kombineres med flere CPU-er – noen ganger på samme brikke, som en heterogen flerkjernet SoC.

Bruk av flerprosessering kan også utnyttes til å forbedre den generelle påliteligheten og sikkerheten. Et problem for alle databaserte design er at de er avhengige av minneteknologier som er sårbare for ioniserende stråling. Når ioniserende stråling treffer silisiumsubstratet i en IC, utløser det en kaskade av frie elektroner som endrer den logiske tilstanden til en transistor. I transistorer i kombinasjonskretser er effekten vanligvis forbigående og fanges bare sjelden opp.

Minner og registre er imidlertid mer sårbare for endringer på grunn av måten de resirkulerer innholdet på for å hindre at lagrede data lekker ut. ECC-koder (Error Checking and Correction) bidrar til å kontrollere problemet. Sannsynligheten for en enkelthendelse øker med minnetettheten, noe som gjør det til et økende problem etter hvert som disse IC-ene skaleres i henhold til Moores lov. Det er heller ikke sikkert at ECC fanger opp alle feilene, noe som kan føre til at et program handler på feil data og til slutt til at kontrollen svikter. I en robot som samhandler med offentligheten kan ikke dette skje.

Redundansteknikker og mangfoldig prosessordesign

Teknikker som redundans løser problemet ved at de enkelte prosessorene kontrollerer hverandres arbeid.

Prosessorene kan være av samme type og kjøre samme kode. Kontrollogikken sammenligner utdataene og bruker stemmegivning for å avgjøre hvilken operasjon som skal tillates, eller krever at operasjonene kjøres på nytt til prosessorene er enige.

Bruken av tre prosessorer med flertallsavstemning er dyrere, men mindre inngripende, ettersom omkjøring av operasjoner kan medføre uønskede forsinkelser. Modulær redundans kan også implementeres på gate-nivå.

Prosessorene i et redundant arrangement trenger ikke å være identiske. I noen arkitekturer brukes en mindre ytelsessterk prosessor som kontrollmotor. I stedet for å kjøre den samme programvaren, utfører den bare konsistenskontroller og tvinger frem en ny kjøring hvis en kontroll mislykkes eller, i mer ekstreme tilfeller, en fullstendig tilbakestilling.

For å minimere sjansene for at systematiske designfeil sniker seg inn i ligningen, kan dupliserte prosessorer designes og implementeres på forskjellige måter. Dette er en teknikk som brukes på enkelte flerkjernede SoC-er utviklet for sikkerhetssystemer i bilindustrien.

Arkitektoniske alternativer for robotdesignere

Robotdesignere kan nå velge mellom et bredt spekter av arkitektoniske alternativer som kan ta dem fra enkle design til svært fleksible maskiner som kan reagere intelligent på problemer og hindringer og fortsette å kjøre problemfritt.