Architektura i konstrukcja współczesnych robotów obejmuje szeroki zakres funkcji i możliwości. Ma to duży wpływ na moc obliczeniową i sposób jej wykorzystania. W kontrolowanym środowisku klatki bezpieczeństwa robot produkcyjny wymaga stosunkowo niewielu zabezpieczeń i może korzystać z prostych strategii sterowania proceduralnego.

Projektanci muszą zadbać o to, by robot przerwał pracę w przypadku otwarcia klatki bezpieczeństwa lub nieprawidłowego ustawienia komponentów. Niemniej jednak wiele wyzwań związanych z bezpieczeństwem można rozwiązać za pomocą prostych blokad sprzętowych, a nie skomplikowanych kombinacji czujników obrazu i oprogramowania. Kluczowe wymagania procesowe w zakresie przetwarzania mają zapewnić efektywne i precyzyjne sterowanie ruchem. Wymaga to przede wszystkim zastosowania mikrokontrolerów lub procesorów sygnału cyfrowego do zarządzania przepływem zasilania do silników i innych elementów wykonawczych.

Ewolucja mikrokontrolerów

Konwencjonalne konstrukcje robotów produkcyjnych nie są na ogół elastyczne. Przed dopuszczeniem robota do pracy każdy program musi zostać skrupulatnie zaprogramowany, poddany symulacji i rygorystycznym testom. W branży produkcyjnej użytkownicy coraz częściej wymagają od robotów większej elastyczności, umożliwiającej szybkie przydzielanie ich do różnych zadań i poruszanie się po hali produkcyjnej bez ograniczeń klatki bezpieczeństwa. Wymagania te wymagają zwiększonej mocy obliczeniowej, aby zapewnić robotowi możliwość bezpiecznego poruszania się, unikając kolizji z obiektami lub obrażeń osób postronnych.

W związku z tym roboty muszą przetwarzać dane z czujników w czasie rzeczywistym i podejmować inteligentne decyzje wraz ze zmieniającymi się warunkami. Wraz z rozwojem ich możliwości poza kontrolowane środowisko hali produkcyjnej, im częściej wchodzą w interakcje z ludźmi, tym większej mocy obliczeniowej wymagają. Roboty usługowe i drony dostawcze muszą być w stanie w inteligentny sposób reagować na złożone sytuacje.

W zaawansowanych scenariuszach pojawia się wyraźne zapotrzebowanie na bardziej zaawansowane oprogramowanie, ściśle powiązane ze zwiększoną przepustowością obliczeniową. Projektanci mają do dyspozycji wiele możliwości zapewnienia niezbędnej mocy obliczeniowej, nie tylko w zakresie wyboru dostawców, ale także ogólnej koncepcji architektonicznej.

Zastosowanie mikrokontrolerów

Jednostka mikrokontrolera (MCU) od dawna stanowi preferowany komponent obliczeniowy w podstawowych zastosowaniach robotyki. Centralnym elementem MCU jest mikroprocesor. Początkowo rdzenie mikroprocesorów były optymalizowane pod kątem prostych operacji arytmetycznych i logicznych, ale od czasu ich wprowadzenia niemal 50 lat temu, wydajność i możliwości obsługi danych znacznie się rozszerzyły. Obecnie rdzenie mikroprocesorów zdolne do natywnego przetwarzania 32-bitowych słów danych i wyposażone w funkcje zwiększające wydajność, takie jak potokowanie i architektura harwardzka, dostępne są obecnie w cenie pozwalającej na ich wykorzystanie nawet w prostych systemach.

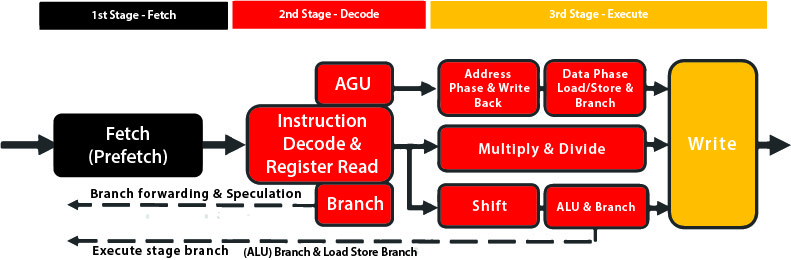

W typowym 32-bitowym rdzeniu mikroprocesorowym, takim jak ARM Cortex-M3, istnieje potok wykonania instrukcji, który rozdziela wykonywanie poleceń na kilka etapów. W potoku M3 najpierw pobierane są instrukcje z lokalnej pamięci podręcznej. Jeśli instrukcji nie ma w pamięci podręcznej, należy ją najpierw załadować z pamięci głównej. Po wejściu w potok bajty instrukcji są dekodowane, aby ocenić, które jednostki funkcjonalne muszą być aktywowane do wykonania instrukcji. Dopiero wtedy następuje wykonanie.

Przetwarzanie potokowe i obsługa przerwań

Przetwarzanie potokowe służy do ukrywania takich aspektów jak opóźnienia pamięci, umożliwiając nakładanie się wykonywania wielu instrukcji i przyczyniając się do zwiększenia szybkości zegara poprzez zmniejszenie liczby kroków logicznych wymaganych na cykl. W przypadku szybszych rdzeni procesorów często stosuje się dłuższe potoki, składające się z dziesięciu lub więcej etapów. Wadą długich potoków jest duże opóźnienie odgałęzień. Jeśli gałąź jest zajęta, ponowne wypełnienie potoku instrukcjami wymaganymi dla nowej gałęzi zajmuje trochę czasu.

Obsługa przerwań umożliwia rdzeniowi procesora tymczasowe wstrzymanie wykonywania programu głównego i zajęcie się innymi zadaniami. Obsługiwanie przerwań jest kluczowym elementem aplikacji, które wymagają reakcji na zdarzenia w czasie rzeczywistym. Bez obsługi przerwań kod programu musiałby zawierać pętle nieustannie wyszukujące informacje o zdarzeniach zewnętrznych, co byłoby znacznie mniej efektywnym wykorzystaniem zasobów obliczeniowych.

Mikroprocesory dla projektantów robotów

System priorytetów stosowany przez większość rdzeni procesorów umożliwia ignorowanie przerwań ze względnie nieważnych urządzeń peryferyjnych, podczas gdy procesor zajmuje się procedurami krytycznymi, takimi jak przekazywanie sterowania z jednego zadania do innego, lub dane wejściowe z krytycznego przerwania. Rezultatem tego jest bardzo elastyczna architektura, która może obsługiwać wiele różnych typów aplikacji w czasie rzeczywistym.

Ważnym i specjalistycznym wariantem mikroprocesora dla projektantów robotów jest procesor sygnałowy (DSP). Jest to rdzeń procesora, który dodaje instrukcje i sprzęt wykonawczy zoptymalizowany pod kątem algorytmów przetwarzania sygnału, takich jak filtry i szybkie transformacje Fouriera. Takie instrukcje obejmują szybkie zabezpieczone operacje mnożenia i dodawania, które można znaleźć praktycznie we wszystkich algorytmach DSP. Ponieważ kod DSP działa na strukturach danych, takich jak macierze i wektory, stosunkowo łatwo jest doprowadzić do pracy równoległej. To z kolei pozwoliło na implementację jednostek wykonawczych SIMD (single instruction, multiple-data), które wykonują te same operacje – takie jak mnożenie i dodawanie – na wielu elementach układu jednocześnie. Dzięki temu uzyskuje się znacznie wyższą prędkość przy stosunkowo niewielkiej złożoności i kosztach.

MCU zawiera szereg zintegrowanych urządzeń peryferyjnych, które są rozmieszczone wokół rdzenia procesora. Zazwyczaj w MCU do zastosowań przemysłowych lub robotycznych, zakres urządzeń peryferyjnych rozciąga się od macierzy pamięci do zaawansowanych, uruchamianych przez liczniki czasowe jednostek, które są wykorzystywane do odciążenia mikroprocesora od konieczności modulacji szerokości impulsu (PWM) z mikroprocesora. PWM jest podstawowym elementem prawie wszystkich strategii sterowania silnikiem, a więc zajmuje istotne miejsce w projektowaniu robotów. Inne urządzenia typu system-on-chip (SoC) dodają kolejne funkcje związane z MCU, takie jak bezprzewodowe nadajniki-odbiorniki, dedykowane szyfrowanie, logika uwierzytelniania i akceleratory grafiki.

Sterowanie i sprzęt

Zastosowanie inteligentnych urządzeń peryferyjnych odzwierciedla coraz popularniejszą zasadę projektowania w robotyce: wykorzystanie rozproszonego sterowania i przyspieszenia sprzętowego. Mikroprocesor może być wykorzystany do sterowania PWM, jednak zwykle stanowi to nieefektywną alokację zasobów. Problem polega na tym, że oprogramowanie musi wielokrotnie przełączać zasilanie pomiędzy tranzystorami w półmostku, który steruje przepływem prądu do silnika w zaprogramowanych odstępach czasowych. Przerwania z zegara czasu rzeczywistego lub licznika czasu mogą łatwo wywoływać programy obsługi, aby przełączyć stan zasilania, a następnie skonfigurować zegar do następnego cyklu. Skutkuje to jednak wysoką częstotliwością przerwań niezwykle prostej sekwencji operacji.

Sterownik PWM łączy w sobie regulator czasowy i układ logiczny przełączania, co eliminuje konieczność przerywania pracy rdzenia mikroprocesora przy każdej operacji przełączania. Oprogramowanie wymaga tylko okresowej aktualizacji liczników czasowych, aby ustawić wymagany cykl PWM. Dzięki stosunkowo niewielkiej ilości dodatkowych układów logicznych, które mogą działać niezależnie od procesora przez długie okresy, znacząco zwiększa się wydajność oprogramowania. To podejście architektoniczne jest zgodne z przyjętym założeniem, obejmującym różne mechanizmy odciążania sprzętu, które mogą zyskać na znaczeniu w projektowaniu robotów. Sprzętowe urządzenia peryferyjne zarządzają częstymi zdarzeniami w czasie rzeczywistym, podczas gdy oprogramowanie ustanawia zasady dla tych urządzeń peryferyjnych.

Wykorzystując sprzętowe urządzenia peryferyjne, projektanci są ograniczeni funkcjami dostarczanymi przez dostawców układów scalonych. Niemniej jednak włączenie sekwencerów bazujących na sprzętowych maszynach stanów może zwiększyć ich wszechstronność. Przykładowo takie sekwencery mogą odczytywać wartości z przetwornika analogowo-cyfrowego, przesyłać wartości danych do pamięci głównej, korzystając z bezpośredniego dostępu do pamięci (DMA), a także konfigurować liczniki czasu, a wszystko bez konieczności angażowania rdzenia procesora. Mimo tych ulepszeń oferowane opcje wciąż mają pewne ograniczenia.

Układy FPGA w robotyce

Bezpośrednio programowalna macierz bramek (FPGA) pozwala na tworzenie niestandardowych urządzeń peryferyjnych, które mogą być zoptymalizowane pod kątem określonych funkcji sterowania robotami i uczenia maszynowego.

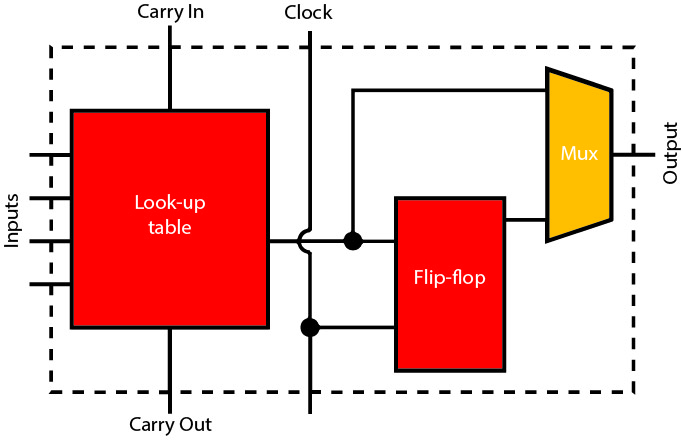

Istotą większości architektur FPGA jest programowalna tabela przeglądowa, dzięki której można zaimplementować dowolną funkcję logiczną, którą można wyrazić jako tabelę prawdy. Korzystając z programowalnych przełączników w strukturze połączeń, tabele przeglądowe są połączone w złożone obwody logiczne. Każda tablica przeglądowa zawiera zazwyczaj jeden lub więcej rejestrów i dodatkowe układy logiczne, takie jak wejścia i wyjścia z łańcucha nośnego, co umożliwia wydajną implementację sumatorów arytmetycznych. Funkcje te tworzą wspólnie blok logiczny, który jest wielokrotnie powtarzany w układzie FPGA.

Ich wadą w porównaniu do w pełni dostosowanych układów logicznych jest znacznie niższa wydajność powierzchni krzemowej. Umieszczenie obwodu logicznego w strukturze FPGA zajmuje od 10 do 20 razy więcej powierzchni krzemowej w porównaniu do niestandardowej implementacji komórki standardowej.

Jednak większość układów FPGA obsługuje przeprogramowanie tablicy logicznej nawet w pracującym systemie. Pozwala to na współdzielenie zasobów dzięki akceleratorom dynamicznie ładowanym do struktury tylko wtedy, gdy są one potrzebne. Podejście to pozwala również na większą elastyczność w projektowaniu końcowym, umożliwiając obsługę nowego sprzętu i dodatkowych funkcji.

Od czasu ich wprowadzenia w latach 80. XX wieku układy FPGA wzbogaciły się o inne funkcje, które poprawiają ogólną gęstość. Bloki pamięci umożliwiają tworzenie buforów i pamięci podręcznych blisko programowalnego układu logicznego. Niedawno dołączyły do nich silniki DSP. W wielu przypadkach silniki DSP są implementowane przy użyciu metody budowania bloków składających się z 8-bitowych lub 16-bitowych jednostek, co umożliwia ich połączenie w celu obsługi danych o większej dokładności.

Jednostki DSP sprawiają, że układy FPGA doskonale nadają się do przetwarzania sygnałów wejściowych z czujników, które wytwarzają duże ilości danych, takich jak kamery, radary i inne rodzaje czujników obrazu. Typowym zastosowaniem jest użycie kombinacji jednostek DSP i akceleratorów logicznych do obsługi algorytmów, takich jak zniekształcanie obrazów i kompensacja oświetlenia, które zapewniają bardziej spójne wejścia do uczenia maszynowego i podobnych funkcji. Funkcje te mogą być koordynowane przez niestandardowe rdzenie mikroprocesorów zaimplementowane w programowalnej strukturze, które działają jako mikrosekwencery dla różnych pierwotnych funkcji przetwarzania.

Wykorzystanie układów GPU, VPU i przetwarzania wieloprocesorowego

Jeszcze inną opcją, szczególnie w przypadku przetwarzania obrazu, jest wykorzystanie procesora graficznego (GPU) lub jednostki przetwarzania obrazu (VPU). Zawierają one dobrze przystosowane do pracy równoległej silniki DSP zoptymalizowane do przetwarzania obrazu. W przypadku robotów, które wymagają bardzo wysokiego poziomu świadomości środowiskowej, te dedykowane jednostki mogą być łączone z wieloma procesorami – czasami na tym samym mikroukładzie, jako heterogeniczny wielordzeniowy SoC.

Zastosowanie wieloprocesowości można również wykorzystać do poprawy ogólnej niezawodności i bezpieczeństwa. Głównym problemem każdego projektu komputerowego jest jego uzależnienie od technologii pamięci, które są wrażliwe na promieniowanie jonizujące. Gdy promieniowanie to dociera do podłoża krzemowego układu scalonego, wyzwala kaskadę wolnych elektronów, które powodują zmianę stanu logicznego tranzystora. W tranzystorach o kombinowanych obwodach efekt ten jest zwykle przejściowy i rzadko wychwytywany.

Jednak pamięci i rejestry są bardziej podatne na zmiany ze względu na sposób, w jaki przetwarzają swoją zawartość, aby zapobiec wyciekowi przechowywanych danych. Kody korekcyjne (ECC) pomagają zwalczać ten problem. Prawdopodobieństwo zakłócenia pojedynczego zdarzenia zwiększa się wraz ze wzrostem gęstości pamięci, co potęguje ten problem, ponieważ układy scalone są nadal skalowane zgodnie z prawem Moore’a. Ponadto kod ECC może nie wychwycić wszystkich błędów, co może doprowadzić do działania programu na podstawie nieprawidłowych danych, a w rezultacie do awarii sterowania. W przypadku robotów wchodzących w interakcje z ludźmi nie można do tego dopuścić.

Techniki redundancji i zróżnicowane konstrukcje procesorów

Techniki redundancji i zróżnicowane konstrukcje procesorów rozwiązują kwestię niezawodności, wykorzystując wiele procesorów do wzajemnej weryfikacji obliczeń.

Procesory te mogą być tego samego typu i wykonywać ten sam kod. Kontrolny układ logiczny porównuje ich wyjścia i wykorzystuje mechanizm głosowania, by zdecydować, na którą operację ma zezwolić, lub wymaga, aby operacje zostały ponownie uruchamiane, dopóki procesory nie osiągną zgodności.

Stosowanie trzech procesorów z głosowaniem większościowym jest bardziej kosztowne, ale mniej inwazyjne, gdyż ponowne uruchamianie operacji może powodować niepotrzebne opóźnienia. Redundancja modułowa może być także realizowana na poziomie bramki.

Procesory w układzie redundantnym nie muszą być identyczne. Niektóre architektury wykorzystują mniej wydajny procesor działający jako silnik sprawdzający. Zamiast uruchamiania tego samego oprogramowania, przeprowadza on kontrolę spójności, inicjuje ponowne wykonanie w przypadku rozbieżności lub, w bardziej krytycznych scenariuszach, uruchamia pełny reset systemu.

W celu zminimalizowania ryzyka systematycznych błędów projektowych zduplikowane procesory mogą być zaprojektowane i implementowane w różny sposób. Jest to strategia stosowana w niektórych wielordzeniowych układach SoC przeznaczonych do samochodowych systemów bezpieczeństwa.

Opcje architektoniczne dla projektantów robotów

Obecnie projektanci robotów mają do dyspozycji wiele możliwości architektonicznych. Opcje te obejmują zarówno proste projekty, jak i wysoce elastyczne maszyny zdolne do inteligentnego reagowania na przeszkody i wyzwania, przy jednoczesnym zachowaniu nieprzerwanej pracy.